M1 ULTRA:除了名字,什么都猜对了

谢知乎数码邀,关于这个事情,我应该说很凑巧而又幸运地再次命中了全部猜测。

只能说,从去年流传到现在的各种 Rumor,几乎都指向了这款产品的存在。

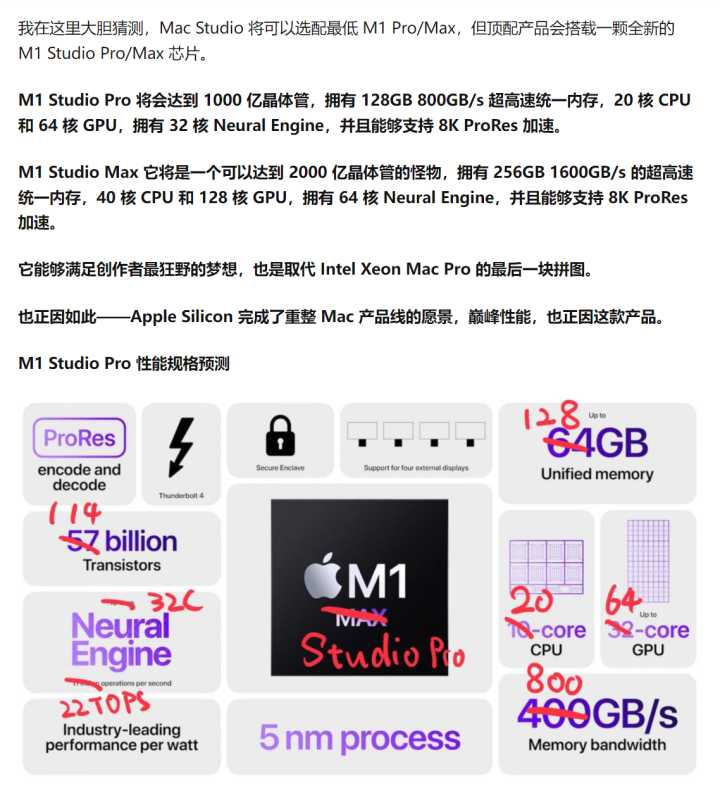

下面是我在发布会前最终猜测篇里对 M1 系列新品芯片的猜测,不能说是完全命中,只能说是一模一样。

欢迎大家到回答下评论:神预言。

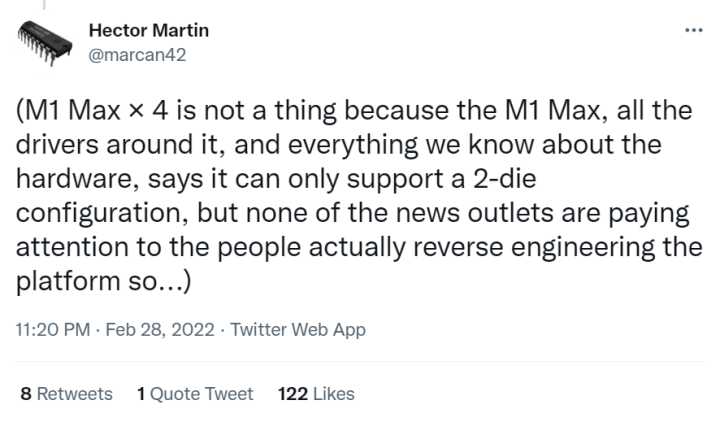

事实上,我对 M1 ULTRA 的猜测可能还要更加狂野一些,我甚至猜想过一个 4-tile 版本的存在,但因为众多原因,最终 M1 ULTRA 的规格定格在了 2-tile。

按照 Hector 的说法,M1 Max 的最大规格也只能做到 2-tile。

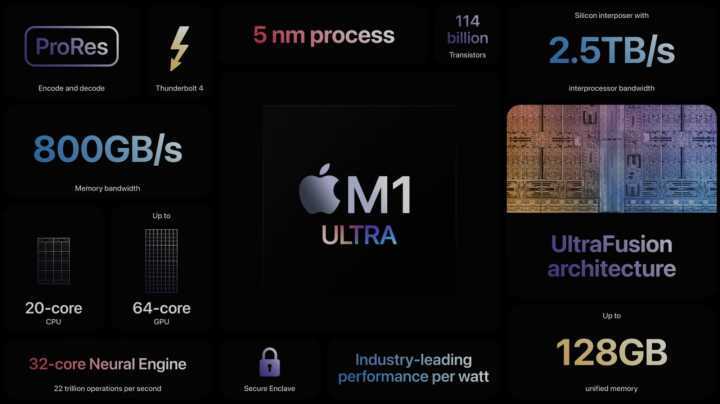

也因为它是一个 MCM(Multi-Chip Module),所以基本上就是给多少 Tile 就有多少性能增加,那翻倍也不是什么令人吃惊的事情,于是你们就看到了这个完全命中的预测:从 CPU 到 GPU 到 NPU 到内存带宽到内存容量,全部都是 2x M1 Max 的规格。

M1 Ultra 本身除了贵以外,并没有什么特别令人吃惊的特性,就是所有东西都从 M1 Max 翻番,无它,但背后的设计却更值得我们了解。

如果你很想知道参数的话,上面已经写了。

MCM Multi-Chip-Module

我们都知道要做更强大的芯片,就需要堆更多的电路,更多的晶体管,但是晶体管多了,良率就会降低,良率低了,那每个芯片就会变得非常昂贵,因此芯片面积或者说规模是不可以无限制的增大的,这也是为什么先进工艺那么重要,工艺越先进,同样的面积就能塞进去更多晶体管,芯片性能上限就越高。

那么在给定的工艺条件下,要想做超越极限的芯片,要怎么办呢?

有一个解决方法就是使用多路。

也就是在同一块主板上使用两块甚至多块 CPU,然后让他们通过主板进行沟通,但这样子显然有很多不利因素,比如占用面积、布线复杂、成本高昂且芯片之间通讯开销巨大。

但当芯片间互联要求没有那么高的时候,多路是一个非常好用的提升性能的解决方案。

比如说图里面显然就是在暗示老对手 Intel 的 Xeon Scalable 产品,这类产品在工作站和服务器中使用得非常多,效果也很不错,但就存在上面说的问题,除此以外,能耗也是一个不容小视的因素。

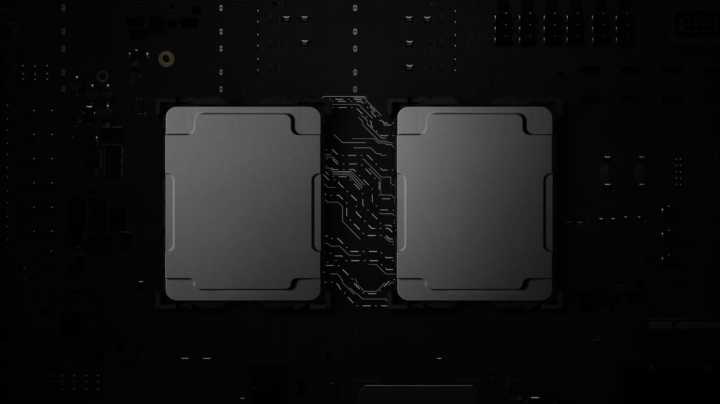

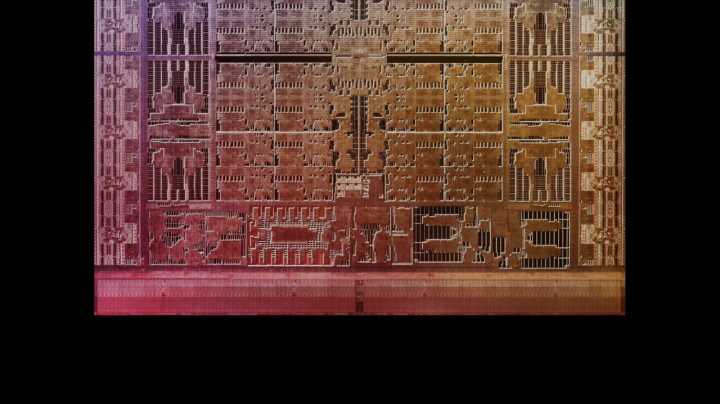

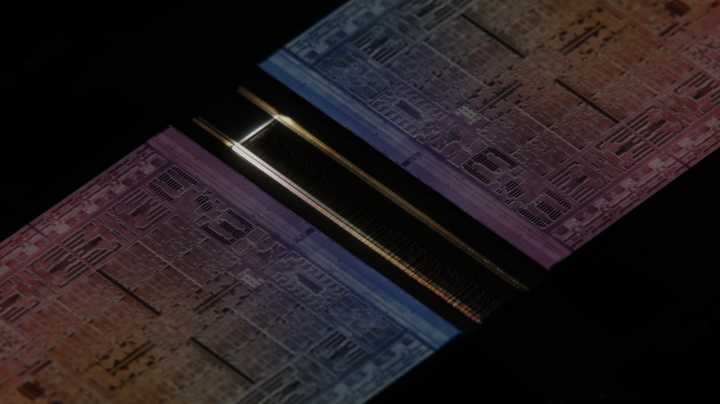

于是苹果的解决方案就是所谓的 UltraFusion 技术,也就是 Die to Die Connection。也就是在芯片设计时在同一个封装(package)里面使用多枚硅片(silicon),并且在其中设计极其高速的互联通道,使得这两块硅片可以形同一块芯片一样共同工作。

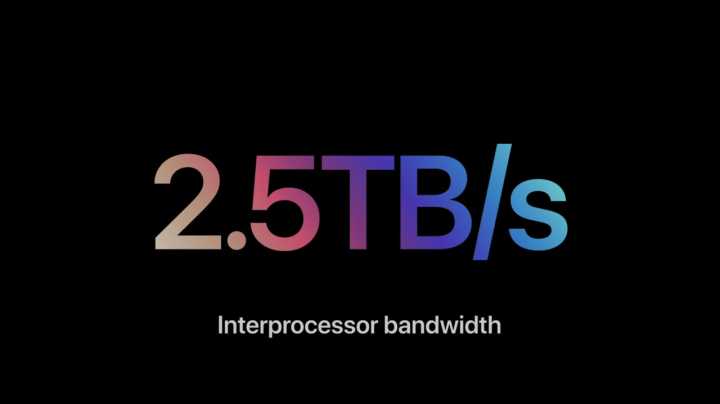

UltraFusion 使用了 1 万条 DTD 连接,提供了高达 2.5TB/s 的互联速度,号称是竞品的 4x。

它的带宽极高、能耗极低,而且由于是数块 die 共同封装,其对良率的敏感度要远低于一块超巨型芯片,因此 DTD 也被认为是未来芯片性能发展的一条具有巨大潜力的道路。

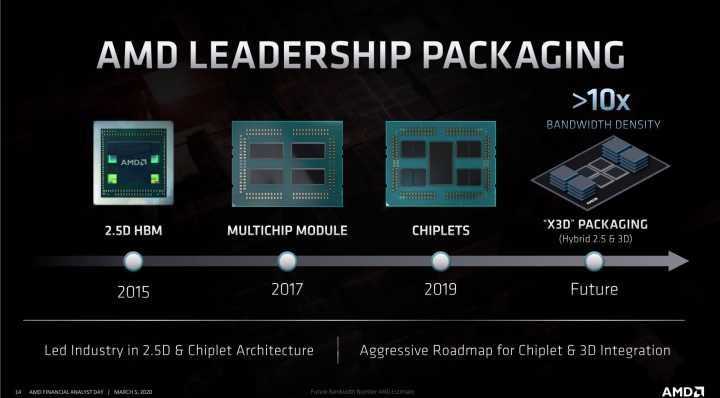

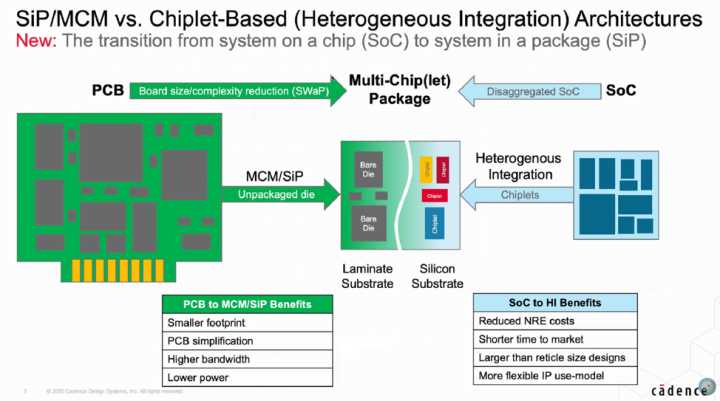

当然这条道路也不是只有苹果在走,AMD 早在 2017 年就引入了 MCM 并且在 2019 年引入了 Chiplet 设计,未来的发展趋势是进一步提升堆叠能力,实现所谓的 3D 堆叠,也就是不仅在 2D 上扩展,还要在垂直方向上扩展。

Intel 夺回一城?M1 Max 能耗 & 绝对性能

我们都知道 Apple Silicon 强调能耗比,也正是因为苹果优秀的架构设计,宽广的架构和很深的流水线,才能实现如此高的 IPC。

因此在每次发布会上,苹果都会强调自己的 PPW,也就是单位能耗性能。

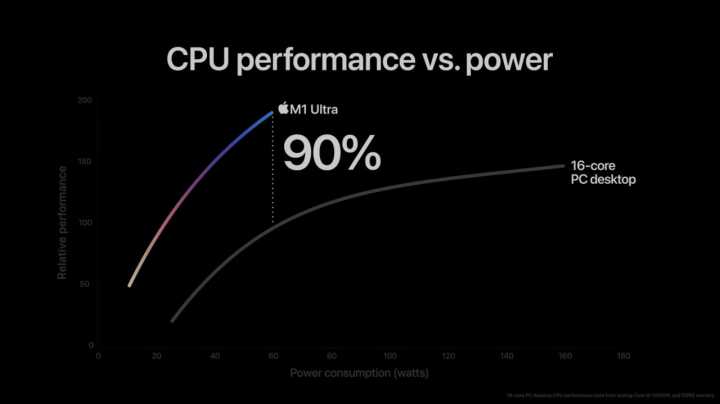

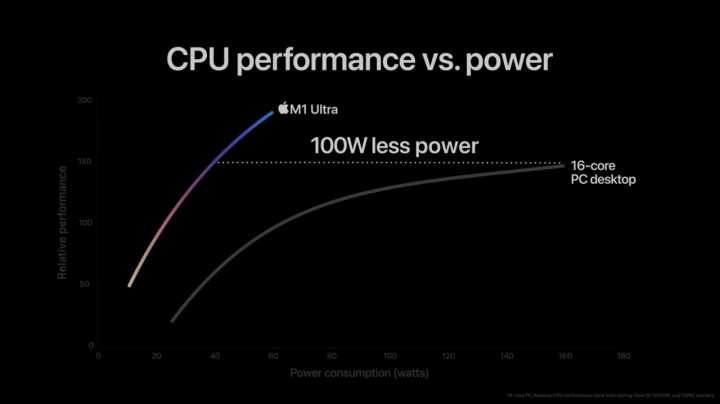

但在这次的发布会里,我们能发现一些有趣的东西,比如 CPU 性能对比的是 12900K。

巧了,我手上用的就是 12900K,M1 Ultra 可以在 60W 的功耗下实现约 12900K 1.9x 的性能,或者说,能在这个时候达到 12900K 160W 时的性能。

但是这个图吧,M1 Ultra 画的是 40W,12900K 画的是 160W,也不知道苹果是反向虚标还是画歪了,姑且认为是 12900K 160W 的性能吧。

这个时候的相对性能是 150% 于 12600K,而我们知道 12900K 在默认状态的 MTP 241W 下,则要比这个性能再高出很多,算换一下不难得知,M1 Ultra 的绝对 CPU 性能是没有 12900K 高的,当然能在 60W 的功耗下实现和 240 W 的 12900K 肩并肩的性能,这本身就是非常了不起的成绩。

这也是为什么 Intel 把能耗比目标放在了 2024+,这两年内,苹果的 PPW 性能依然会可以预测地领先,但绝对性能上,Intel 靠着大小核心的 Hybrid 设计,用 10nm SF+ 单 die 高频硬刚 MCM 的 M1 Ultra,也同样是设计与工艺的另一种巅峰平衡。

正如我在之前的预测文章中所说:

苹果是一家记仇的公司。

这么说可能不太合适,让我们换个说法——苹果是一家有执念的公司。想当年,因为 PowerPC 阵营能耗比不行,苹果 Mac 产品线被迫整体迁移到 Intel 的 x86/64,在经历了这么多年后,当苹果选择再次转换阵营,从 x86/64 转为 Apple Silicon 的时候,在工业设计上毫不掩饰地将新款的 MacBook Pro 设计得与 Power Mac 时代的 PowerBook G4——无比相似。我们都知道 Apple 在从 x86/64 转向 Apple Silicon 的计划是两年,而现在正是第二个年头。

在苹果的愿景里,是有一类达到甚至超过目前主流桌面端的性能、且能耗仅介于笔记本和桌面端的产品。它能够满足创作者最狂野的梦想,也是取代 Intel Xeon Mac Pro 的最后一块拼图。也正因如此——Apple Silicon 完成了重整 Mac 产品线的愿景,巅峰性能,也正因这款产品。

M1 ULTRA 成就了这款产品,也因此 Mac Studio 以 Power G4 Cube 的形态回归。

Chiplet 和 MCM

当然 MCM 并不是芯片发展的唯一方向,另一个非常受欢迎的方向就是将不同的 Chiplet 封装在同一块 silicon substrate 上,也就是所谓的 HI。

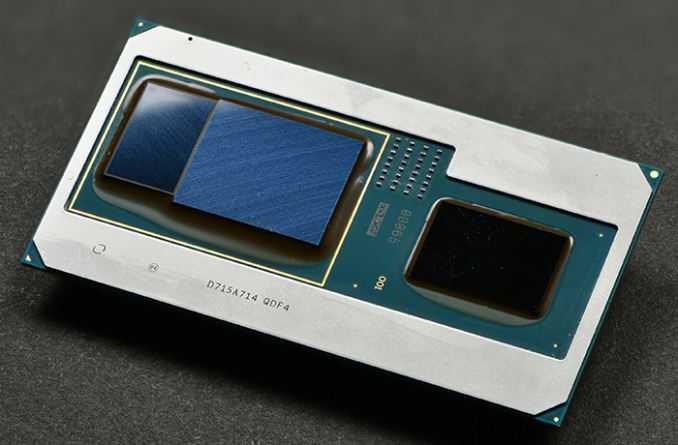

比如说此前 Intel 在 Kaby Lake G 上封装 AMD GPU 和 Intel CPU 于同一 substrate 上的设计,也可以被认为是一种 chiplet。

民用千亿晶体管,以及 MCM 未来的应用

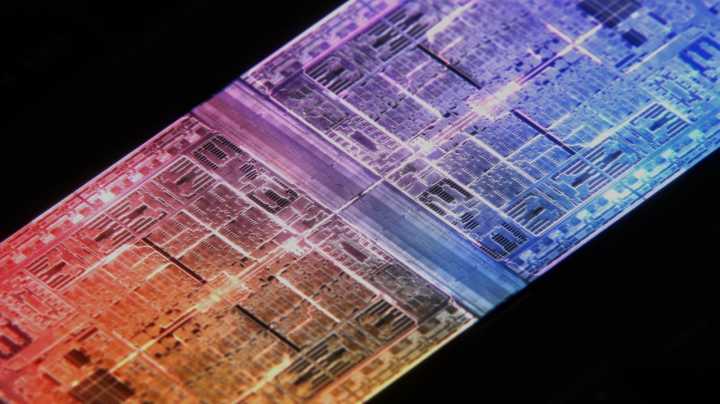

另一个值得注意的是,本次 Apple 的 M1 Ultra 突破了千亿晶体管大关,尽管这不是芯片行业第一次突破千亿晶体管大关,但却是消费级应用首次落地。

此前 Intel Xe HPC 代号为 Ponte Vecchio 芯片也实现了上下两个部分的 chiplet,搭配 HBM 存储 chiplet 和 EMIB 连接,并应用了 Foveros 3D 堆叠技术。

但这款产品咕咕咕到现在,也没正式落地,反而是 M1 Ultra 以 TSMC 5nm 工艺率先突破了千亿晶体管大关。

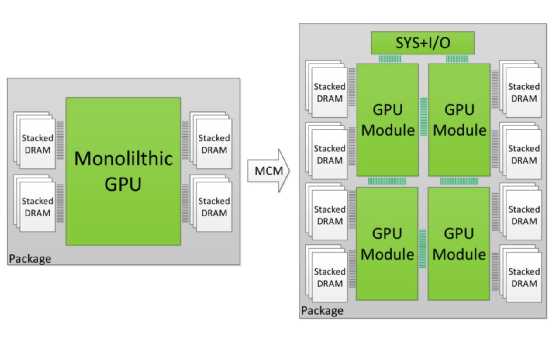

早在 2017 年,英伟达也探讨过 MCM-GPU 的可行性,并认为 MCM-GPU 可能是未来的发展方向,更有传闻说 RTX 40 系列(Hopper)显卡将使用 MCM 设计来降低生产成本和提高良率,以实现后摩尔时代 IP 复用弹性的提高。

未来

M1 Ultra 说实在的并不让我激动,可能是因为我早已期待它的到来。

它的到来对于半导体行业来说,简单、粗暴、有效。

一点都不优美,但是非常有用。

苹果靠自己走通了高 IPC IP(P-Core 和 E-Core)如何覆盖从手持移动设备(A 系列)到桌面端(M 系列)的全面覆盖,同一个核心架构从 A14 用到 M1 用到 M1 Pro 用到 M1 Max 用到 M1 Ultra,覆盖从 iPhone SE 到 iPhone 13 mini/13/13 Pro 到 iPad mini 到 iPad Air 到 iPad Pro 到 MacBook Air/Pro 到 Mac mini 到 iMac 到 Mac Studio,往死里用,绝不浪费。

到更证明了只要产品力足,什么高性能先进工艺成本高企,那都不是事儿。

但显然,我们都知道还有一个 4-tile 的版本,那个才是 M1 时代的究极大 boss。

或许会叫 M1 Extreme 吧……

过几个月就知道了。

MCM 走通了,Chiplet 走通了,我们很快就会看到大家用起来,AMD 的 CPU 已经用上了、Intel 的 14 代酷睿、Xe HPC、NVIDIA 的新显卡……

单 die 的时代或许已经过去,多芯堆叠的时代序幕正在拉开。

简单,粗暴,但有效

有钱就是可以任性